# Choose the Right Logic Analyzer Clocking Mode

### Introduction

High-speed synchronous digital buses are changing in many ways. Not only are they increasing in speed, but also they are changing in the way the data is transferred. Gone are the days when data was transferred on the rising edge of the main bus clock. In the never-ending pursuit of improved data throughput, emerging synchronous digital buses send data multiple times per cycle using a diverse array of clocking schemes. Synchronous data transfers are becoming ever more common in emerging computing, networking, and communications architectures. With this trend comes an urgent requirement for efficient digital acquisition tools that can assist engineers in their troubleshooting and verification work.

To keep pace with the trend toward high-speed synchronous digital buses, today's logic analyzers must offer great flexibility in clocking and triggering. They must be able to capture data without the use of external devices to "pre-condition" the data before it enters the instrument itself. To meet the needs of digital designers confronting time-to-market and technical challenges, logic analyzers need to have complex synchronous clocking capabilities built into the data acquisition system's front end.

The Tektronix TLA700 Series logic analyzers include a wealth of clocking capabilities to address all of the data transfer methods outlined above, including source-synchronous clocking.

This application note will explain how to use these specialized clocking features to acquire data from complex high-speed synchronous data buses, including source-synchronous buses.

### Challenges in Capturing Today's High Speed Digital Buses

In their pursuit of ever-increasing data throughput in PCs, servers, and communications equipment, designers have learned that simply increasing the base clock rate is no longer enough to achieve higher bandwidth. Departing from basic edge-triggered clocking, in which data transfers on the leading edge of each cycle's clock pulse, digital architects have devised a number of alternative approaches:

- One bit of data transfers on two edges (leading and trailing) in each cycle

- Two bits of data transfer on one edge in each cycle (double-pumped data)

- Two bits transfer on two edges in each cycle (quad-pumped data)

- "Multiple" bits transfer with a special strobe signal rather than a clock

Application Note

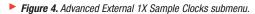

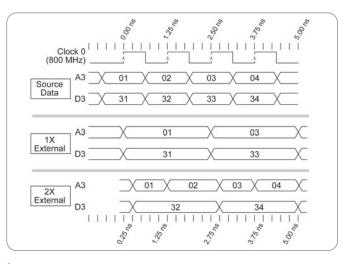

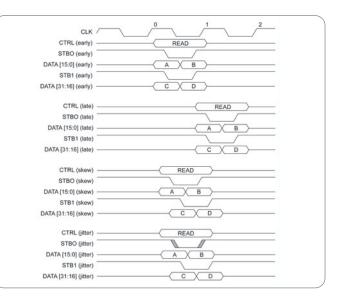

The latter method is known as source-synchronous clocking architecture. This approach is gaining wider acceptance and will be the focus of some application examples later in this document. In a typical source-synchronous transaction, the transmitting device sends data multiple times within each cycle, along with a strobe associated with each data group. The receiving device uses this strobe to latch the data, then resynchronizes the data to the master or common clock. Some DDR memory buses and front side buses, as well as AGPnX graphics cards use this technique. DDR memories have an equivalent data transfer rate up to 800 MT/s and front side buses have an equivalent transfer rate up to 533 MT/s. Figure 1 shows the timing relationships among the signals involved in a typical source synchronous data transfer.

Another method of improving data bandwidth is to reduce the number of data channels, multiplex the data, and increase the synchronous clock frequency substantially. To achieve these higher clock frequencies, the data is sent differentially and at reduced signal amplitudes. High-speed buses implementing this scheme include Rapid I/O, whose data transfer rates range from 100 MT/s to 2 GT/s, and HyperTransport, with data rates ranging from 400 MT/s to 2 GT/s.

The tools needed to capture data from the foregoing types of buses consist primarily of logic analyzers and oscilloscopes. With proper connections to the bus and observing high-speed digital design rules, data can be presented to the logic analyzer or oscilloscope with good signal integrity.

While most of today's logic analyzers are capable of capturing this high-speed data, there is almost always a requirement for an

Figure 1. Typical source synchronous data transfer.

external pre-processor on the front end to "pre-condition" the data so the analyzer can interpret the newer data protocols. Pre-conditioning is necessary because the logic analyzer lacks the complex clocking capabilities needed to interpret the high speed synchronous 2X, 4X and source synchronous data protocols that are now prevalent in today's digital buses.

Pre-conditioning tools take up valuable lab space and are timeconsuming to setup. They also latch the data, making it impossible to see the raw timing of the digital or analog signals. This makes it difficult to find timing and analog problems.

Oscilloscopes are also powerful debug tools, but their channel count is limited. It can be very time-consuming to find the four critical signals that will reveal an elusive timing bug. But the oscilloscope is very good at finding analog integrity-related problems, if the instrument has direct access to the data bus. This capability is now

| Clocking Mode                                                 | Measurement/Application                                               | Typical System under Test                                           |

|---------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------|

| 1X Internal (asynchronous)                                    | Waveform views, not synchronized with SUT events                      | General-purpose digital measurements with<br>clock rates to 500 MHz |

| 2X Internal (asynchronous)                                    | Waveform views, not synchronized with SUT events                      | General-purpose digital measurements with<br>clock rates to 1 GHz   |

| 4X Internal (asynchronous)                                    | Waveform views, not synchronized with SUT events                      | General-purpose digital measurements with<br>clock rates to 2 GHz   |

| <b>1X External</b> (synchronous)<br>One edge                  | Waveform and listing views, synchronized with SUT events              | FSB, conventional edge-clocked devices                              |

| <b>1X External</b> (synchronous)<br>Two edges                 | Acquisition double or quad-pumped data (requires demux)               | AGP2X (double-pumped) AGP4X (quad-pumped)                           |

| <b>1X External</b> (synchronous)<br>Two edges ("quad-pumped") | Slower quad-pumped data acquisition using demux                       | Quad-pumped FSB architectures                                       |

| 2X External (synchronous)<br>One edge                         | Fast acquisitions with two data bits per cycle clocked<br>by one edge | Rambus memory architecture                                          |

| <b>2X External</b> (synchronous)<br>Two edges                 | Acquisition of two data bits per cycle, one from each clock edge      | Double Data Rate (DDR) memory devices and buses                     |

| <b>4X External</b> (synchronous)<br>Two edges ("quad-pumped") | Fastest quad-pumped acquisition (to 1.25 Gb/s)                        | RapidIO, HyperTransport, other high-speed<br>comm buses             |

| Source Synchronous<br>Edge-independent                        | Acquisition of strobe-dependent data rather than clocked data         | DDR, AGP2X, AGP4X, AGP8X                                            |

Table 1. Available clocking modes for the Tektronix TLA700 Series logic analyzers.

Application Note

available with the iLinkTM Tool Set capability that couples TLA700 Series logic analyzers with TDS5000/6000/7000 Series oscilloscopes. Many oscilloscope models can be interfaced to TLA700 Series logic analyzers to acquire signals through the logic analyzer probes and display time-correlated analog waveform views on the logic analyzer display.

### Advanced Clocking Features Support Asynchronous and Synchronous Bus Acquisitions

The Tektronix TLA700 Series logic analyzer with TLA7Axx advanced logic acquisition module provides a feature set that addresses the all of the prevalent high-speed synchronous acquisition requirements. Table 1 equates the full range of TLA700 Series logic analyzer clocking modes with the device clocking approaches discussed earlier. Internal (asynchronous) clocking modes are used for timing acquisitions only and are not covered in this document, but are included here for the sake of comprehensiveness.

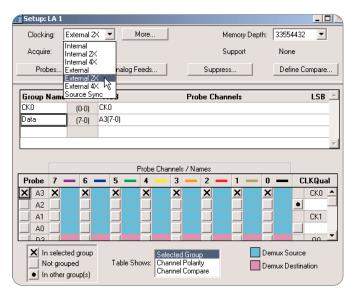

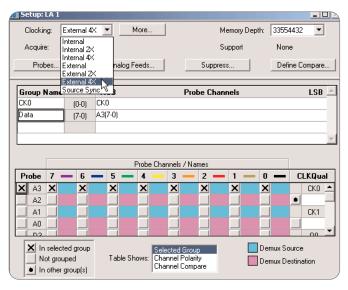

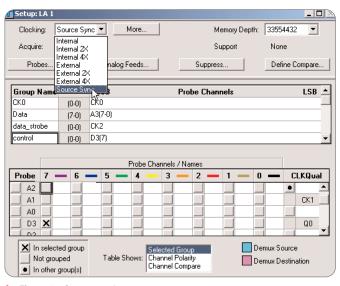

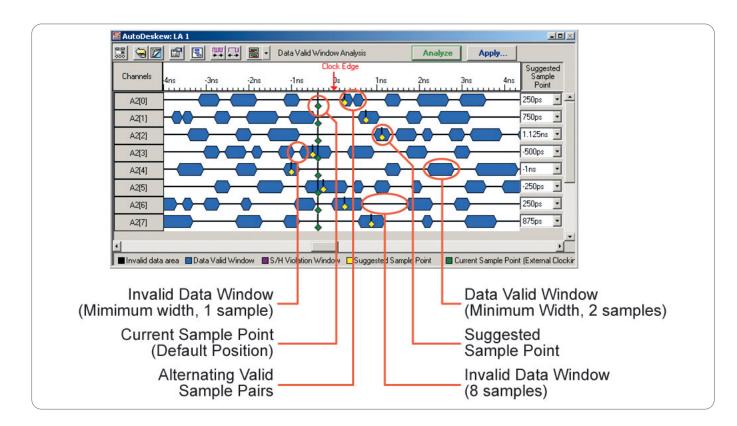

The TLA7Axx setup menu in Figure 2 shows a pull-down menu with the available clocking mode selections.

### Characteristics of the TLA7Axx Clocking Modes

### Internal Clocking (1X, 2X, 4X)

Each internal (asynchronous) clocking mode offers a unique combination of clock rate, channel count, and memory depth. 1x internal clocking, for example, is ideal for capturing data from busses and devices that are relatively "slow" but very wide. In the 1x mode, the logic analyzer can acquire data on up to 136 channels (per acquisition module) at once. In contrast, 4x internal clocking is best suited for work with very fast, narrower busses that may generate many millions of data cycles in normal operation. The 8 GHz MagniVu<sup>TM</sup> timing feature is always active, irrespective of the clock mode.

### **1X Internal**

- Default internal clock rate is 500MHz (2 nsec)

- Maximum acquisition depth: up to 64M samples for very long timing acquisitions

- Sample clock can be user-adjusted from 2 nsec to 50 msec

### **2X Internal**

- Equivalent internal clock rate is 1 GHz (1 nsec)

- Memory depth is doubled to 128M samples

- Two-way demultiplexing of the data cuts channel width in half

- Data display provides a "normalized" view of the data

- EasyTrigger provides a variety of trigger templates to simplify trigger setup

| Setup: LA 1           |                          |                          |

|-----------------------|--------------------------|--------------------------|

| Clocking: Interr      | nal 💌 2ns 💌              | Memory Depth: 67108864 💌 |

|                       | nal 2X                   | Support None             |

| Probes Exter<br>Exter | rnal 2X                  | Suppress Define Compare  |

| Group Name            | ce Sync Pr               | robe Channels LSB 📥      |

|                       | 0-0) CK0                 |                          |

| A3 (7                 | 7-0) A3(7-0)             |                          |

| A2 (7                 | 7-0) A2(7-0)             |                          |

|                       |                          | •                        |

|                       |                          |                          |

|                       | Probe Channels / N       |                          |

| Probe 7 💻             | 6 - 5 - 4 - 3 -          | 2 — 1 — 0 — CLKQual      |

| • A3 •                | • • • •                  | • • • СКО •              |

| • A2 •                |                          | • • • × -                |

| A1                    |                          | CK1                      |

| A0                    |                          |                          |

|                       |                          |                          |

| Not grouped           | Table Shows: Channel Pol | arity                    |

Figure 2. TLA7Axx Setup menu with available clocking modes.

### **4X Internal**

- Allows the sampling of the data at clock rates up to 2 GHz (500 psec)

- Memory depth extends to 256M samples

- Four-way demultiplexing technique supports up to 136 channels by merging four acquisition modules.

- Data display provides a "normalized" view of the data

- EasyTrigger provides a variety of trigger templates to simplify trigger setup

### External Clocking (1X, 2X, 4X)

External (synchronous) clocking is the key to acquiring data most efficiently; each sample equates to a specific clock event on the bus and the resulting data can be used to reconstruct detailed listings of bus activity as well as timing diagrams. While massive memory depth still a desirable attribute, it is less critical than in the internal clocking modes because only events are recorded—not the passage of time between them.

Like the internal clocking modes, there are three basic external clocking modes.

### **1X External (Synchronous)**

- Clock rates up to 450 MHz with full channel count

- Effective maximum data rate is 450 Mb/s

### 2X External (Synchronous)

- Clock rates up to 800 MHz with channel count reduced by half.

A special 2X synchronous circuit on the logic analyzer's front end enables this function

- Effective maximum data rate is 800 Mb/s

Application Note

### **4X External (Synchronous)**

- Maximum clock speed is 625 MHz

- Channel count depends on multiplexing scheme used

- Effective maximum data rate is 1250 Mb/s

#### **Overview of the Clocking Menus**

Figure 3 shows an example of the basic clocking menu for the External 1X clocking mode. The clocking equation can use up to four OR'ed clocks, and each of these clocks may be AND'ed with up to three qualifiers.

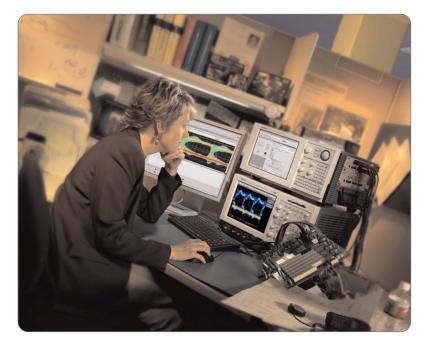

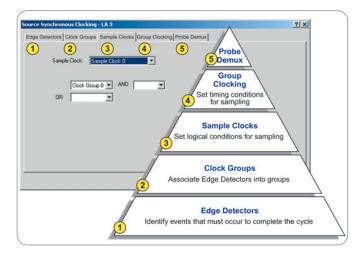

Beyond the basic clocking capabilities of the TLA7Axx module there are advanced clocking features, accessed via the "Advanced Clocking" button at the bottom of the window. Figure 4 shows the resulting display: the Advanced External 1X Sample Clocks window. The same Sample Clocks submenu exists, but a second Sample Clock choice is available on a pull-down, allowing you to set up two different sample clock equations. In Figure 4, Sample Clock 1 is the master clock.

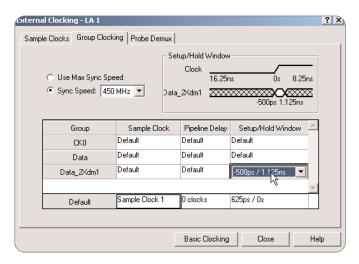

Looking again at Figure 4, note that two additional tabs—Group Clocking and Probe Demux—have appeared. Clicking the Group Clocking tab produces the screen shown in Figure 5. Here you can define "Group" information that includes the sample clocks associated with the group, the number of clock pipeline delays (up to seven) for the group, particular channel group, and the setup/hold sample window.

The 625 psec setup/hold sample window, adjustable in 125 psec steps, ranges from +16.125 ns setup to +8.375 ns hold relative to the selected clock edge. You may select the maximum synchronous clock speed available or you may choose slower speeds, either 235 MHz or 120 MHz. This clocking mode is useful for capturing complex buses with large channel counts and multiple data qualifiers.

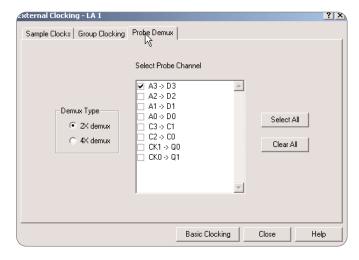

The last tab on the External Clocking window brings up the Probe Demux submenu, Figure 6. Here you can individually select which channel groups to demultiplex (either two-way or four-way). In addition there are buttons to select all or none, respectively.

| Clocking - LA 1    | ?×                           |

|--------------------|------------------------------|

| Sample Clocks      |                              |

|                    |                              |

| Clock Definition:  |                              |

| CIUCK D'ennicion.  |                              |

|                    |                              |

| J CKO 🔽 AND QO     | ▼ AND Q1 ▼ AND Q2 ▼          |

| OR 🗾 CK1 💌 AND Q1  | ▼ AND Q2 ▼ AND Q3 ▼          |

| OR 1 CK2 - AND /Q0 | ▼ AND /Q1 ▼ AND /Q2 ▼        |

| OR 1 CK3 💽 AND /Q1 | ▼ AND /Q2 ▼ AND /Q3 ▼        |

|                    |                              |

|                    |                              |

|                    |                              |

|                    |                              |

|                    | Advanced Clocking Close Help |

Figure 3. External 1X Basic Clocking submenu.

| Clocking - LA 1                          | ? ×  |

|------------------------------------------|------|

| Sample Clocks Group Clocking Probe Demux |      |

|                                          |      |

| Sample Clock: Sample Clock 1             |      |

| Sample Clock 1<br>Sample Clock 2         |      |

| I CKO V AND QO V AND Q1 V AND Q2         | - I  |

| OR 🖌 CK1 💌 AND Q1 🔍 AND Q2 🔍 AND Q3      | - I  |

| OR 🗾 CK2 💌 AND /Q0 💌 AND /Q1 💌 AND /Q2   | - I  |

| OR 🖌 CK3 💌 AND /Q1 🔍 AND /Q2 💌 AND /Q3   | -    |

|                                          |      |

| Note: Sample Clock 1 is the master clock |      |

|                                          |      |

| Basic Clocking Close                     | Help |

|                                          |      |

| Externa | l Clocking - LA 1     |                |                | ? ×                 |

|---------|-----------------------|----------------|----------------|---------------------|

| Sampl   | e Clocks Group Clocki | ng Probe Demux |                |                     |

|         |                       | Set            | up/Hold Window | ,                   |

|         | 🔿 Use Max Sync Spe    | ed             | Clock          | 5ns Os 8.375ns      |

|         | 235                   | MHz            | Default 😿      | 625ps 0s            |

|         | Group                 | Sample Clock   | Pipeline Delay | Setup/Hold Window 📥 |

|         | CK0                   | Default        | Default        | Default             |

|         | A3                    | Default        | Default        | Default             |

|         | A2                    | Default        | Default        | Default             |

|         |                       |                |                | <b>v</b>            |

|         | Default               | Sample Clock 1 | 0 clocks       | 625ps / 0s          |

|         |                       |                |                |                     |

|         |                       |                | Basic Clocking | Close Help          |

Figure 5. Advanced External 1X Group clocking submenu.

Application Note

### External 2X

External 2X Clocking (Figure 7) is a multiplexed format that supports the TLA7Axx module's highest possible clock rates. Edge spacing within any one signal can be as little as 1.25 ns. In this mode you can select up to four different clock sources. Each source can be set to respond the rising edge, the falling edge, or both. Here the 625 psec setup/hold sample window ranges from +8 ns setup to +8.375 ns hold relative to the selected clock edge. Using the External 2X clocking mode you might, for example, sample a set of multiplexed data (double pumped data) at two different times with synchronous clock rates up to 800 MHz and double data rates up to 800 Mb/s.

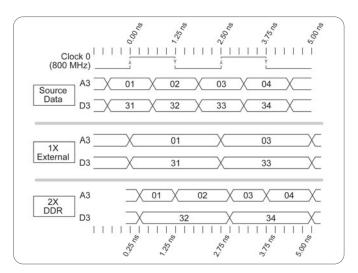

Figure 8 shows the advantage of external 2X clocking when compared to 1X clocking. Using standard 1X clocking on the 800 MHz SUT in the uppermost set of waveforms, exactly half of the data is lost because samples are taken at 2.5 ns intervals rather than 1.25 ns. With 2X clocking, two groups work together to sample twice as frequently. The data in D3 is meaningless but A3 contains every bit of data the SUT produces on the A3 channel (similarly, the 4X mode combines the resources of four channels to support full acquisition on one channel). If it is necessary to see the true output of D3 as well, then it cannot be paired with A3 like this; both must be separately paired with spare channels that can share their sampling resources.

A second method of External 2X clocking is aimed at DDR requirements. Here, the data is captured on both edges of the clock rising and falling. The maximum clock rate is equal to the base sync speed of the TLA7Axx module—450 MHz. To implement External 2X DDR clocking, you need only make the proper choices in the Clocking menu, as shown in Figure 16 later in this document. Note that the "Clock edge" button (near the CKØ pull-down) shows two edges active, in contrast to the standard 2X clocking menu shown earlier.

In the 2X DDR mode, the clock duty cycle does not have to be symmetrical but it does have to be free of unwanted transients and aberrations. Should a random glitch get into the signal, it will register as a valid edge and cause erratic misalignments of the acquisition data.

The next step up is External 4X Clocking. Here you have the choice of up to four different clock sources, each one using either the rising or falling edge. For this clocking mode, the 625 psec setup/hold sample window ranges from +8 ns setup to +7.625 ns hold relative to the selected clock edge.

| external Clocking - LA 1                                                                                                     |                                                                                                                                                                                                                                                                                                                |                |        | ? ×  |

|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------|------|

| External Clocking - LA 1         Sample Clocks       Group Clocking         Demux Type         © 2% demux         C 4% demux | Probe Demux<br>Select Probe C<br>E3 $\Rightarrow$ E1<br>$\forall$ E2 $\Rightarrow$ E0<br>A3 $\Rightarrow$ 02<br>$\forall$ A1 $\Rightarrow$ D1<br>A0 $\Rightarrow$ D0<br>C3 $\Rightarrow$ C1<br>$\forall$ C2 $\Rightarrow$ C0<br>CK3 $\Rightarrow$ Q2<br>$\forall$ CK2 $\Rightarrow$ Q3<br>CK1 $\Rightarrow$ 00 |                | Select | AI   |

|                                                                                                                              |                                                                                                                                                                                                                                                                                                                | Basic Clocking | Close  | Help |

Figure 6. Advanced External 1X Demux submenu.

| xternal 2X Clocking -                           | LA 1       |         | ?) | X |

|-------------------------------------------------|------------|---------|----|---|

| Clock edge: <u></u>                             | CK0 🔽      |         |    |   |

| Setup/Hold Wind                                 | w          |         |    |   |

| Clock                                           |            |         |    |   |

| 8ns                                             | Os         | 8.375ns |    |   |

| Default 🔀                                       |            | *****   |    |   |

|                                                 | 625ps 0s   |         |    |   |

| The maximum clock<br>mode is 800 MHz /<br>Group |            |         |    |   |

| СКО                                             | Default    |         |    |   |

| A3                                              | Default    |         |    |   |

| A2                                              | Default    |         |    |   |

|                                                 |            | -       |    |   |

| Default                                         | 625ps / Os |         |    |   |

|                                                 |            |         |    |   |

| Close                                           | _          | Help    |    | , |

Figure 7. External 2X Clocking submenu.

Figure 8. Comparison of External 2X timing results with a basic1X acquisition.

Application Note

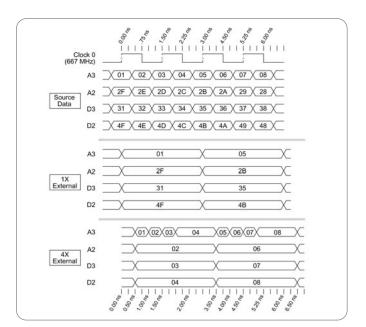

In the External 4X Clocking submenu there is a four-way demux and a second edge delay to program. The first setup/hold window adjustment is relative to the rising or falling edge of the user-selected clock. The second edge delay adjustment is the delay after the first clock edge. Using the External 4X Clocking mode you can sample a set of multiplexed data (quad pumped data) at four different times up to 625 MHz and quad data rates up to 1.25 Gb/s. Figure 9 shows the External 4X Clocking submenu.

As we have seen in this overview of clocking modes, each mode matches the needs of a particular SUT clocking architecture. The TLA700 Series logic analyzer has kept pace with the needs of emerging bus architectures, offering a steady stream of enhancements in speed, clocking options, triggering features, and bus support since its introduction.

Selecting the right acquisition mode for your SUT is a matter of assessing the frequency and data rate requirements, plus the synchronization functions ranging from common leading-edge-clocked to quad pumped and source sync. The balance of this document is devoted to examples that summarize the steps needed to implement these external clocking modes: 1X, 2X, 4X, and source synchronous, with particular emphasis on the latter mode.

### Step-by—Step Application Examples: Clock-Synchronous Buses

### 2X External Clocking

The typical target device for the 2X External mode, also known as the Fast Clock mode, is one that uses a single edge to clock data at very high speeds—up to 800 MHz.

Begin by selecting "2X External" on the "Clocking" pull-down menu on the Setup page as in Figure 10. Designate the clock and data Probe Channels appropriately to match the probes and pins you have connected to your device.

Next, go to the "Clock edge" pull-down in the Clocking window (Figure 11). Select CKO from the available signal names previously entered on the Setup page, and using the button next to the pull-down, choose the single rising. Edit any Setup/Hold values as needed, or accept the defaults.

| c xter | rnal 4X ( | Clocking - | LA 1                                            |                         | ? ×      |

|--------|-----------|------------|-------------------------------------------------|-------------------------|----------|

|        |           | Clock ea   | lge: <u>J</u> CKO                               | •                       |          |

|        |           | Setup/Ha   | ld Window                                       |                         |          |

|        |           | Cloc       | k0s                                             | 750ps                   |          |

|        |           | Defau      | ilt 🗙 🗘                                         |                         |          |

|        |           |            | dge Delay of 750ps and<br>e would be 1.33 Gb/s. | l a symmetric, periodic | _        |

|        | G         | roup       | Setup/Hold Window                               | Second Edge Delay       | <u>^</u> |

|        | 0         | СКО        | Default                                         | Default                 |          |

|        |           | A3         | Default                                         | Default                 |          |

|        |           | A2         | Invalid Group                                   | Invalid Group           |          |

|        |           |            | ^                                               |                         | -        |

|        | De        | efault     | 625ps / Os                                      | 750ps                   |          |

|        | [         | Close      |                                                 | Help                    |          |

Figure 9. External 4X Clocking submenu.

Figure 10. 2X External Mode Setup page.

| xternal 2X Clocking                | - LA 1   |            |          | ?     | X |

|------------------------------------|----------|------------|----------|-------|---|

| Clock edge:                        | <u>ı</u> | (0 💌       |          |       |   |

| - Setup/Hold Wi                    | ndow —   |            |          |       |   |

| Clock 8                            | ns       |            | 8.25ns   |       |   |

| Default 💈                          |          | 625ps Os   | *****    |       |   |

| The maximum clo<br>mode is 800 MH: |          | 1b/s.      |          | )<br> |   |

| Group                              |          | Setup/Hold | Window 🕮 |       |   |

| CKO                                |          | Default    |          |       |   |

| Data                               | Î        | Default    |          |       |   |

|                                    |          |            | ¥        |       |   |

| Default                            |          | 625ps / Os |          |       |   |

| Close                              |          |            | Help     |       |   |

Figure 11. 2X External mode clocking window.

Application Note

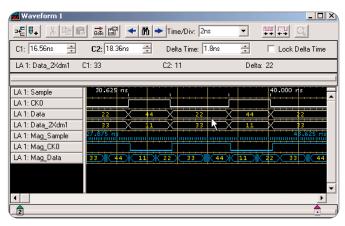

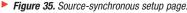

Figure 12 is the waveform view that results from this 2X External acquisition, and Figure 13 is the listing of the same data. In the waveform view, the line titled "LA1: Mag\_Sample" shows a series of tick marks, each representing 125 ps of time. The total time between any two rising edges of the CK0 signal is 1.625 ns, so the logic analyzer records a valid data state on every 1.625 ns increment of time.

This fast (2X) clocking mode has a special characteristic that must be kept in mind, as the waveform view in Figure 12 shows. The system software places the timestamp of the second sample in the cycle 1 ns after the first sample is taken. This is necessary because the timestamp machine runs at a maximum frequency of 500 MHz (a 2 ns period) and the software must pick a delay that describes when the second edge sample occurred. This value is 1 ns.

### 2X External, Double Pumped

Some devices "double-pump" their data: they drive data on every edge, rising or falling, of a master clock signal. Here again the 2X External mode is the solution. The frequency limit for this mode is 450 MHz, but since the device is double-pumping, the net data rate is 900 Mb/s. Like the basic 2X mode described previously, the system adds 1 ns "separator" increments after the first sample in each cycle. A typical timing scheme for this mode appears in Figure 14.

| 🖶 Waveform 1      |            |                   |                   | _ D ×             |

|-------------------|------------|-------------------|-------------------|-------------------|

| <u>≁</u> ∎. X 🖻 I | 1 🖬 🗗 🛉    | 🕈 🕅 🔸 Time/Div: 1 | ns 🔻              |                   |

| C1: -200ns 🔅      | C2: 200ns  | 🗧 🕼 🕄 ta Time:    | 400ns 🔹           | 🗌 Lock Delta Time |

| LA 1: CK0         | C1:        | C2: 0             | Delt              | a:                |

|                   |            |                   |                   |                   |

| LA 1: Sample      | 809.000 hs |                   |                   | 815.750 ns        |

| LA 1: CK0         |            |                   |                   |                   |

| LA 1: Data        | X          | FF X 00           | Ţ <u>X </u> ĘĘ,X, | X                 |

| LA 1: Mag_Sample  | 808.000 ms | <u></u>           | . <u> </u>        | 815.875 ns        |

| LA 1: Mag_CK0     |            |                   |                   |                   |

| LA 1: Mag_Data    | FF         |                   | FF 00             |                   |

|                   |            |                   |                   |                   |

|                   |            |                   |                   |                   |

|                   |            |                   |                   |                   |

| •                 |            |                   |                   |                   |

|                   |            |                   |                   |                   |

Figure 12. 2X External mode acquisition results waveform view.

|                  | Listing 1                                                                              |                                                                                   |                                                                                  |                                                                                                                                                                                                                                                                                                                                              |                     |

|------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| n <sup>¥</sup> r | 1 🗣 🐰 🖻 🛛                                                                              |                                                                                   |                                                                                  | A A 🛉 🕅 🕈 🚮                                                                                                                                                                                                                                                                                                                                  |                     |

|                  | 1: 0 📫                                                                                 | C2:                                                                               |                                                                                  | Delta Time: 2.375ns                                                                                                                                                                                                                                                                                                                          | 🕂 🗌 Lock Delta Time |

| LA               | 1                                                                                      | LA                                                                                | 1                                                                                |                                                                                                                                                                                                                                                                                                                                              |                     |

|                  | Sample                                                                                 | СК0                                                                               | Data                                                                             | Timestamp                                                                                                                                                                                                                                                                                                                                    |                     |

|                  | 37<br>38<br>39<br>40<br>41<br>42<br>43<br>44<br>45<br>46<br>47<br>48<br>49<br>50<br>51 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 00<br>FF<br>00<br>FF<br>00<br>FF<br>00<br>FF<br>00<br>FF<br>00<br>FF<br>00<br>FF | 1.000 ns<br>2.375 ns<br>1.000 ns<br>2.375 ns |                     |

| U                | 1                                                                                      |                                                                                   |                                                                                  | 2,375 //3                                                                                                                                                                                                                                                                                                                                    |                     |

Figure 13. 2X External mode acquisition results listing view.

Figure 14. 2X External "double-pumped" timing.

► Application Note

As before, the process begins with selecting "External 2X" and assigning the physical connections on the Setup page (Figure 15).

The Clock menu (Figure 16) too is similar to that of the basic 2X mode, except we use the "Clock edge" button to choose the symbol representing a pair of edges. The waveform and listing views, Figures 17 and 18 respectively, summarize the results of the acquisition.

### **External 4X Clocking**

Quad-pumped devices deliver data four times in each SUT cycle. The TLA700 Series provides an External 4X clocking mode that is ideal for this type of device. In addition, it is possible to acquire quad-pumped data using a combination of the basic External ("1X") mode and demultiplexing. We will cover both approaches here.

| 🕼 Setup: LA 1 |                                        |         |           |               |             |           |         |

|---------------|----------------------------------------|---------|-----------|---------------|-------------|-----------|---------|

| Clocking:     | External 2>                            | < 🔹 🗌   | More      |               | Memory Dept | n: 335544 | 32 💌    |

| Acquire:      | Internal<br>Internal 2X<br>Internal 4X |         |           |               | Support     | None      |         |

| Probes        | External                               | nalo    | g Feeds   | Supp          | oress       | Define    | Compare |

|               | External 2×<br>External 4×             | X W     |           |               |             |           |         |

| Group Nam     | Source Syr                             | nc      |           | Probe Ch      | annels      |           | LSB 📥   |

| CKO           | (0-0)                                  | CK0     |           |               |             |           |         |

| Data          | (7-0)                                  | A3(7-0) |           |               |             |           |         |

|               |                                        |         |           |               |             |           |         |

|               |                                        |         |           |               |             |           | -       |

|               |                                        |         |           |               |             |           |         |

|               |                                        |         | Probe Cha | nnels / Names |             |           |         |

| Probe 7       | - 6 -                                  | - 5 -   | - 4       | 3 🗕 2 🛛       | - 1         | 0 —       | CLKQual |

| 🗙 A3 🗙        | ×                                      | ×       | ×         | X X           | X           | ×         | СКО 🔺   |

| A2            |                                        |         |           |               |             |           |         |

| A1            |                                        |         |           |               |             |           | CK1     |

|               |                                        |         |           |               |             |           |         |

| A0            |                                        |         |           |               |             |           |         |

| A0            |                                        |         |           |               |             |           |         |

Figure 15. 2X Double-pumped mode setup page.

| xternal 2X Clocking - LA 1                                 | ? ×                                                           |

|------------------------------------------------------------|---------------------------------------------------------------|

| Clock edge: <u>I</u>                                       | ко 🔽                                                          |

| Setup/Hold Window                                          |                                                               |

| Clock 8ns                                                  | 0s 8.25ns                                                     |

| oris<br>Default 🔀                                          | 625ps 0s                                                      |

| The maximum clock rate<br>mode is 450 MHz / 900 I<br>Group | / data rate for this clocking<br>Mb/s.<br>Setup/Hold Window 🖆 |

| СКО                                                        | Default                                                       |

| Data                                                       | Default                                                       |

|                                                            | •                                                             |

| Default                                                    | 625ps / 0s                                                    |

| Close                                                      | Help                                                          |

Figure 16. 2X Double-pumped mode clock menu.

| 📇 Waveform 1     |            | N                     |               |    |       | _ <b>_ _</b> X    |

|------------------|------------|-----------------------|---------------|----|-------|-------------------|

| <u></u>          | 1 👬 🖆 🗹    | <mark>- 06 →</mark> 1 | Nme/Div: 1n   | s  | •     |                   |

| C1: 1ns 🗧        | C2: 1ns    | ÷                     | )elta Time: 2 | ns | *     | 🔲 Lock Delta Time |

| LA 1: CK0 (      | C1: 1      | C2                    | 2: 1          |    | Delta | a: O              |

|                  |            |                       |               |    |       | 1                 |

| LA 1: Sample     | 816.625 ns |                       |               | 1  |       | 828.375 ns        |

| LA 1: CK0        |            |                       |               |    |       |                   |

| LA 1: Data       | 00 X       | FF                    | X 00          | X  | FF    |                   |

| LA 1: Mag_Sample | 816.000 hs |                       |               |    |       | 828.750 ns        |

| LA 1: Mag_CK0    |            |                       |               |    |       |                   |

| LA 1: Mag_Data   | FF         | 00                    | FF            |    | 00    | FF X              |

|                  |            |                       |               |    |       |                   |

| •                |            |                       |               |    |       | Þ                 |

| <b>.</b>         |            |                       |               |    |       | <b>1</b>          |

Figure 17. 2X Double-pumped mode waveform view.

Application Note

### Acquiring Quad-Pumped Data Using the External 4X Mode

Figure 19 is a conceptual timing diagram for the basic 4X External mode.

As of Version 4.2 TLA Series software, the system displays the 4X data on A3 as follows: the first two samples are evenly spaced at 500 ps intervals; the third sample is placed 500 ps after the second sample. The fourth sample uses up the remaining time in the cycle.

By selecting "External 4X" on the Setup page (Figure 20), you can achieve the highest data rates available from the TLA700 Series logic analyzer—more than 3X the maximum clock rate of the TLA7Axx module; up to 1.25 Gb/s. This mode is well suited to today's high-speed digital communication buses.

|                  | isting 1                                                                                     |                                                                              |                                                                                              |             |                                                                                                                                                                                                          |   |                   |

|------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------------|

| n <sup>¥</sup> n | 1 <b>- X</b> - <b>1</b>                                                                      | 8 5                                                                          |                                                                                              | ×  A  ♠   ₥ | op<br>Code                                                                                                                                                                                               |   |                   |

| C1<br>LA         | : 0 ÷                                                                                        | C2:<br>LA                                                                    |                                                                                              | ÷ Delta     | Time: 4.375ns                                                                                                                                                                                            | • | 🗌 Lock Delta Time |

|                  | Sample                                                                                       | СК0                                                                          | Data                                                                                         | Timestamp   |                                                                                                                                                                                                          |   | <b>^</b>          |

|                  | 37<br>38<br>39<br>40<br>41<br>42<br>43<br>44<br>45<br>46<br>47<br>48<br>49<br>50<br>51<br>51 | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | FF<br>00<br>FF<br>00<br>FF<br>00<br>FF<br>00<br>FF<br>00<br>FF<br>00<br>FF<br>00<br>FF<br>00 | Le.         | 1.000 ns<br>2.375 ns<br>1.000 ns<br>2.250 ns<br>1.000 ns<br>2.375 ns<br>1.000 ns<br>2.375 ns<br>1.000 ns<br>2.375 ns<br>1.000 ns<br>2.375 ns<br>1.000 ns<br>2.375 ns<br>1.000 ns<br>2.375 ns<br>1.000 ns |   |                   |

Figure 18. 2X Double-pumped mode listing view.

Figure 19. 4X External timing diagram.

Figure 20. 4X mode setup page.

Application Note

This mode works by sampling twice on each clock edge from the SUT. The normal Setup/Hold parameters dictate sampling on the leading edge of the clock. To capture the data from the trailing edge, you must set a delay value that tells the logic analyzer when to look for the edge. In Figure 21, the "Second Edge Delay" is 750 ps. As this Clock page explains, the theoretical data rate is 1.33 Gb/s. This is a calculated number; note that TLA700 performance beyond 1.25 Gb/s is not guaranteed.

The waveform and list views showing the results of the 4X External mode acquisition are shown in Figures 22 and 23, respectively. In Figure 23, note that the system has again placed "separators" after the first sample in each cycle. In this 4X mode, the system defaults to add 500 ps, between the samples (in contrast to the 1 ns added by both 2X modes).

| cxter | nal 4X Clocking - I | LA 1                                            |                         | ? X |

|-------|---------------------|-------------------------------------------------|-------------------------|-----|

|       | Clock eo            | lge: <b>ʃ</b> CKO                               | •                       |     |

|       | ⊢ Setup/Ho          | ld Window                                       |                         |     |

|       | Cloc                | k0s                                             | 750ps                   |     |

|       | Defau               | ilt XXX XXX<br>625ps Os                         |                         |     |

|       |                     | dge Delay of 750ps and<br>e would be 1.33 Gb/s. | l a symmetric, periodic |     |

|       | Group               | Setup/Hold Window                               | Second Edge Delay 📥     |     |

|       | CK0                 | Default                                         | Default                 |     |

|       | Data                | Default                                         | Default                 |     |

|       |                     |                                                 | V                       |     |

|       | Default             | 625ps / Os                                      | 750ps                   |     |

|       | Close               |                                                 | Help                    |     |

Figure 21. 4X mode clocking page.

| 🖶 Waveform 1                      |           |                                       |                 |        |          |             |

|-----------------------------------|-----------|---------------------------------------|-----------------|--------|----------|-------------|

|                                   | 1 🚮 🗗 🗹   | - 🕅 🔸 Time/D                          | iv: 500ps       | •      |          | ୍କ          |

| C1: -300ps                        | C2: 300ps | 🗧 Delta Ti                            | me: 600ps       | •      | C Lock [ | ) elta Time |

| LA 1: CK0                         | C1: 0     | C2: 0                                 |                 | Delta: | 0        |             |

|                                   |           |                                       |                 |        |          |             |

| LA 1: Sample                      | 5.625 ns  | · · · · · · · · · · · · · · · · · · · |                 |        | +        | 9.000 ns    |

| LA 1: CK0<br>LA 1: Data           |           |                                       |                 |        |          |             |

|                                   | 5.125 ns  | <u>, X FF X</u>                       | <u>, oo.</u> X  |        |          | 9.000 ns    |

| LA 1: Mag_Sample<br>LA 1: Mag_CK0 |           | <u> </u>                              | <u>.   .   </u> |        |          |             |

| LA 1: Mag_UNU                     |           |                                       |                 |        | ho       |             |

| LA I: Mag_Data                    |           | XX <u>00</u>                          |                 |        |          |             |

|                                   |           | K                                     |                 |        |          |             |

|                                   |           |                                       |                 |        |          | •           |

| •                                 |           |                                       |                 |        |          | •           |

| <b>_</b>                          |           |                                       |                 |        |          |             |

Figure 22. 4X mode waveform view.

| <b>A</b>   | Listing 1  |          |           |                          |      | _ <b>_ _ _ _ _</b> |

|------------|------------|----------|-----------|--------------------------|------|--------------------|

| <u>n</u> ¥ | n 🏝 🐰 🗈    | G        | 🖹 🔺 A 🛉 🕅 | ♦ Jore                   |      |                    |

| C          | 1: 0 🗦     | C2:      | 4 🗧 Delta | Time: 3.25               | ns 🕂 | 🗌 Lock Delta Time  |

| U          | A1         | LA 1     |           |                          |      |                    |

| Π          | Sample     | Data     | Timestamp |                          |      |                    |

|            | 82<br>83   | 00<br>FF |           | 00 ps                    |      |                    |

|            | 84         | 00       | 1.        | 875 ns                   |      |                    |

|            | 85<br>86   | FF<br>00 |           | <i>500 ps</i>  <br>00 ps |      |                    |

|            | 87         | FF       |           | 500 ps                   |      |                    |

|            | 88<br>89   | 00<br>FF |           | 750 ns<br>500 ps         |      |                    |

|            | 90<br>91   | 00<br>FF |           | 00 ps                    |      |                    |

|            | 92         | 00       | 1,        | 875 ns                   |      |                    |

|            | 93<br>94   | FF<br>00 |           | <i>500 ps</i><br>00 ps   |      |                    |

|            | 95         | FF       |           | 500 ps                   |      |                    |

|            | 96<br>. 97 | 00<br>FF |           | 875 ns<br>500 ps         |      | <b>_</b> _         |

| U          |            |          |           |                          |      |                    |

Figure 23. 4X mode listing view.

Application Note

# Acquiring Quad-Pumped Data Using the Demultiplexing Method

The second method of acquiring data from a quad-pumped SUT doesn't actually use the 4X External mode. Instead, it uses the basic (1X) External mode and demultiplexing techniques to capture four data events per cycle. This mode is preferred when the clock speeds are below 450 MHz. Figure 24 shows the Setup page. Note that "External" is selected here, not "External 4X."

Continuing on the Setup page, right-click the field named "Data" in the Group Names column. This produces a pull-down menu from which you can specify either a 2X or a 4X demux (demultiplex) group, as seen in Figure 25. Choosing "Create 2X Demux Group" sets up the logic analyzer to use a pair of channels on the specified edges, doubling the effective acquisition rate.

Move to the first tab of the clocking page (Figure 26). CKO is designated as the master clock, and you must choose a logical OR condition for its edges. Either the rising edge OR the falling edge will clock valid data.

| 🖌 Setu | p: LA 1              |                                                     |         |           |                                |                |            | >              |

|--------|----------------------|-----------------------------------------------------|---------|-----------|--------------------------------|----------------|------------|----------------|

| Cloc   | :king:               | External                                            | •       | More      |                                | Memory Dep     | oth: 33554 | 432 💌          |

| Acq    | uire:                | Internal<br>Internal 2×                             |         |           |                                | Support        | None       |                |

| F      | robes                | Internal 4×<br>External<br>External 2<br>External 4 | x hs na | log Feeds | Sup                            | press          | Defir      | e Compare      |

| Grou   | p Name               | Source Sy                                           | nc3     |           | Probe C                        | hannels        |            | LSB            |

| СКО    | -                    | (0-0)                                               | CK0     |           |                                |                |            |                |

| Data   |                      | (7-0)                                               | A3(7-0) |           |                                |                |            |                |

| Data   | _2×dm1               | (7-0)                                               |         | D3(7),D   | 3(6),D3(5),D3(4),              | D3(3),D3(2),D3 | 8(1),D3(0) |                |

|        |                      |                                                     |         |           |                                |                |            |                |

|        |                      |                                                     |         |           |                                |                |            |                |

|        |                      |                                                     |         | Probe Cha | annels / Names                 |                |            |                |

| Prob   | e 7                  | - 6 •                                               | - 5     | - 4       | 3 — 2                          | - 1            | 0 —        | CLKQual        |

| XA     | з 🗙                  | ×                                                   | X       | ×         | XX                             | ×              | ×          | ско 🔺          |

|        | .2 🔄                 |                                                     |         |           |                                |                |            | •              |

| A      | .1                   |                                                     |         |           |                                |                |            | CK1            |

|        | .00                  |                                                     |         |           |                                |                |            |                |

|        | 2 6                  |                                                     |         |           |                                |                |            |                |

| ×      | In select<br>Not gro | ted group                                           | Tat     |           | lected Group<br>annel Polarity |                | Demux So   |                |

|        | -                    | r group(s)                                          | 1 di    |           | annel Compare                  |                | Demux De   | stination<br>/ |

Figure 24. Quad pumped mode setup page 1.

| 🚺 Setup: LA | 1                                        |             |                                                         |                |            |

|-------------|------------------------------------------|-------------|---------------------------------------------------------|----------------|------------|

| Clocking:   | External                                 | ▼ More      | Memory                                                  | / Depth: 33554 | 4432 💌     |

| Acquire:    | Normal                                   | •           | Suppor                                                  | t Non          | e          |

| Probes      |                                          | Analog Feed | s Suppress                                              | Defi           | ne Compare |

| Group Na    | me                                       | MSB         | Probe Channels                                          |                | LSB 📥      |

| CK0         | (0-0)                                    | СКО         |                                                         |                |            |

| Data        | Undo                                     | Ctrl+Z      |                                                         |                |            |

|             | Add Group                                |             |                                                         |                |            |

|             | Delete Grou                              | D           |                                                         |                |            |

|             | Delete All Gr                            | oups        | e Channels / Names                                      |                |            |

| Probe       | Demux Grou                               | ips 🕨       | Create <mark>R</mark> X Demux Group                     | 0 -            | CLKQual    |

| 🗙 A3 🚽      | Cut                                      | Ctrl+X      | Create 🗛 Demux Groups                                   | ×              | ско 🔺      |

| A2          |                                          | Ctrl+C      | Delete 2X Demux Group                                   |                | •          |

| A1          | Paste                                    | Ctrl+V      | Delete 4X Demux Groups                                  |                | CK1        |

| A0          | Select All                               |             |                                                         |                |            |

| Not g       | elected group<br>grouped<br>her group(s) | Table Shows | Selected Group<br>: Channel Polarity<br>Channel Compare | Demux So       |            |

Figure 25. Quad pumped mode setup page showing additional menu selections.

| external Clocking - LA 1                 |                |       | ? X  |

|------------------------------------------|----------------|-------|------|

| Sample Clocks Group Clocking Probe Demux |                |       |      |

| Sample Clock: Sample Clock 1             | •              |       |      |

| S CKO AND                                | •              |       |      |

| OR 1 CKO - AND                           | •              |       |      |

| 0R 💌                                     |                |       |      |

|                                          |                |       |      |

|                                          | R              |       |      |

| Note: Sample Clock 1 is the master clock |                |       |      |

|                                          |                |       |      |

|                                          | Basic Clocking | Close | Help |

Figure 26. Quad pumped mode sample clock page.

Application Note

On the Group Clocking tab (Figure 27), it is critical to set up the proper timing on the demux data group (Data\_2Xdm1). The Setup/Hold timing setting on this group determines when the logic analyzer looks for the later of the two data samples associated with each edge.

The final step is the Probe Demux tab, shown in Figure 28. Select "2X Demux" (since this is what we specified on the Setup page) and check "A3  $\rightarrow$  D3" in the "Select Probe Channel" window.

Figures 29 and 30 show the waveform and listing views, respectively, from the quad-pumped data acquisition. On the listing page, note that half of the data resides in the "Data\_2xdm1" column, while the other half occupies the "Data" column. This is an arbitrary assignment that does not affect the acquisition outcome. The placement in the columns is entirely dependent on when the logic analyzer acquisition actually starts.

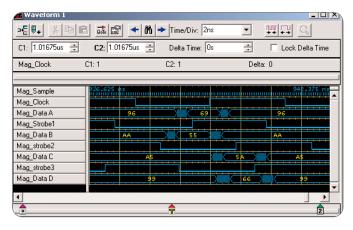

#### Step-by-Step Application Examples: Source-Synchronous Buses

To capture data from a source synchronous bus, you must use a dedicated source-synchronous acquisition mode. All of the modes discussed up to this point rely on a conventional clock signal to clock data into the logic analyzer. The source synchronous uses dedicated strobe signals instead of, or sometimes in addition to, a normal clock pulse. The TLA700 Series logic analyzer, alone among instruments of its type, can address this need without external interfaces to pre-process the data.

Source synchronous architecture is gaining popularity in digital systems, and designers are likely to encounter it more frequently in the future. For this reason, and because source synchronous acquisition is inherently more complex than other modes, the balance of this document is devoted to two detailed source sync application examples. Specifically, the examples include:

- **Example 1:** acquisition with a master clock, one data strobe, and Return-t0-Zero (RZ) data format.

- **Example 2:** acquisition with a master clock, three data strobes, and Double Data Rate (DDR) data.

### Two Kinds Of Source Synchronous Transfers

Before proceeding with an explanation of clocking, it is necessary to understand the differences between Type 1 and Type 2 source synchronous data transfers.

**Type 1** buses use data strobes to transfer data, as described in and earlier discussion in this document and illustrated in Figure 1. Some of the leading source synchronous buses today are: AGP (2X, 4X, and 8X); Intel® IA32 front side bus (Pentium® 4); and Intel IA64 front side bus (Itanium®).

Figure 27. Quad-pumped mode group clocking page.

Figure 28. Quad pumped mode probe demux page.

Figure 29. Quad pumped listing page.

Application Note

Common characteristics of Type 1 source synchronous buses include:

- Data rates between 133 MT/s and 800 MT/s

- Multi-drop

- Bidirectional

- One common-clock domain (for control)

- At least one source-synchronous strobe domain (for address and data)

- Multiple strobe groups per source-synchronous strobe domain

- Undefined skew between strobe groups

- Non-persistent strobes (edges only occur when there is valid data)

- Most Type 1 buses include an explicit bus reset signal.

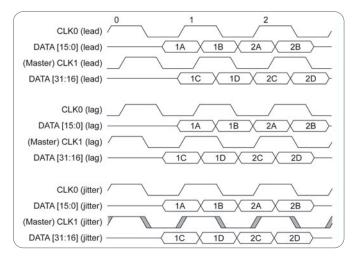

In general, source-synchronous data must be demultiplexed and synchronized with the common-clock data for triggering and analysis. Determining which clock frame to associate with the demultiplexed data is perhaps the biggest challenge when acquiring data from Type 1 buses. Figure 31 depicts some of the variables that can affect the acquisition. Early signals, late signals, skewed data, or jittery strobes can impact the acquisition. In TLA Series logic analyzers, MagniVu acquisition can help resolve these small but important timing deviations.

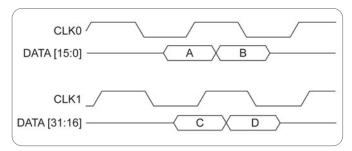

**Type 2** source synchronous transfers take a different approach. There are no strobes, as shown in Figure 32.

Examples of Type 2 buses include HyperTransport, RapidIO (8- and 16-bit), and POS-PHY4. Common characteristics of Type 2 buses are as follows:

- Data rates ranging from 200 MT/s and 2 GT/s.

- Point-to-point

- Unidirectional

- No separate common clock domain

- Only one source synchronous clock domain

- One or more clock groups

- Undefined skew between clock groups

- Persistent clocks (edges appear with or without valid data)

- No explicit bus reset signal

It is necessary to demultiplex and synchronize the source synchronous data across all groups for triggering and analysis. The challenge here, as before is to correctly determine which clock frame to associate with each data pump. With buses that have only one clock group (POS-PHY4 and RapidIO 8-bit, for example) this is not a problem.

| Histing 1                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                      |                    |                                                                                                                                                                         |                                                                                 |                 |

|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------|

| <u> % @</u>                                                                                  | 8 🚮 🖬 🔺                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A                                                                                                                    | M 🕴 🛷 op           |                                                                                                                                                                         |                                                                                 |                 |

| C1: 0 🛨                                                                                      | C2: 2<br>LA 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -                                                                                                                    | Delta Time: 6.75ns | •                                                                                                                                                                       | Γ                                                                               | Lock Delta Time |

| Sample                                                                                       | Data_2×dm1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Data                                                                                                                 | Timestamp          |                                                                                                                                                                         |                                                                                 |                 |